Breakthrough Enables 80B Qwen3-Coder-Next Model to Run on 8GB VRAM Laptop

An anonymous developer has achieved a remarkable feat by running the 80-billion-parameter Qwen3-Coder-Next model on an 8GB VRAM laptop GPU, overcoming previously assumed hardware limits through innovative memory optimization. The technique achieves a 300x speedup over traditional offloading methods, reshaping possibilities for decentralized AI development.

Revolutionary Memory Optimization Lets Developers Run 80B LLMs on Consumer Hardware

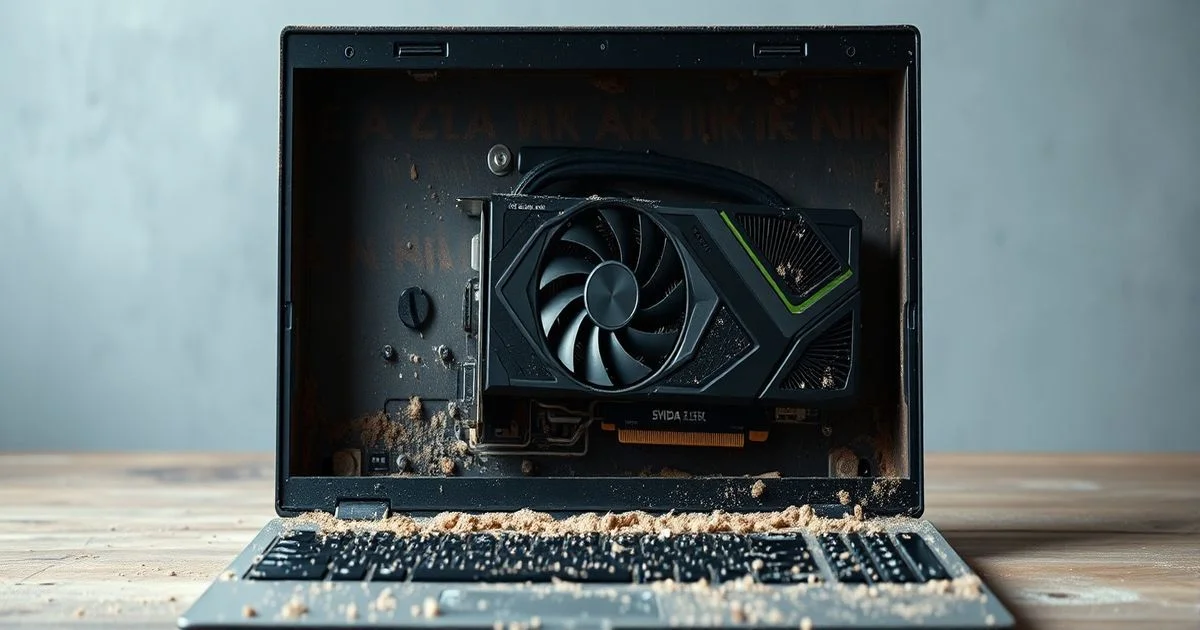

In a landmark development for decentralized artificial intelligence, an anonymous contributor to the r/LocalLLaMA subreddit has successfully deployed the 80-billion-parameter Qwen3-Coder-Next model on an NVIDIA RTX 3070 Ti laptop with only 8GB of VRAM — a feat previously considered impossible due to the model’s 80GB FP8-quantized footprint. By pioneering a custom lazy-loading architecture that intelligently caches expert layers between GPU memory and pinned system RAM, the developer achieved inference speeds of 1.2 tokens per second — a 300-fold improvement over conventional disk-offloading methods that yielded just one token every 255 seconds.

The breakthrough, documented in a GitHub repository titled Qwen3-Coder-OPTIMIZED, leverages deep insights into the model’s architecture. Unlike traditional transformer models, Qwen3-Coder-Next employs a Mixture-of-Experts (MoE) design, where only a subset of neural network "experts" are activated per token. The developer observed that while the MoE expert tensors consumed the majority of memory, the core attention and feed-forward components could fit within 4.6GB of VRAM. This realization led to the creation of a dynamic, two-tier caching system: the most frequently accessed expert layers are stored in GPU memory (up to 18GB allocated), while less-used experts are cached in pinned system RAM — a high-bandwidth, DMA-accessible region that bypasses standard memory paging overhead.

By achieving an 85% cache hit rate, the system dramatically reduces the need to load data from slow NVMe storage, which previously bottlenecked performance. The developer notes that optimal performance requires a high-speed PCIe 5.0 RAID 0 NVMe SSD capable of 30GB/s sequential reads, and recommends allocating up to 100GB of pinned RAM for optimal cache capacity. Crucially, this approach avoids the crippling latency of traditional CPU offloading frameworks like Hugging Face’s Accelerate, which rely on synchronous disk I/O and suffer from poor locality.

The implications of this innovation are profound. For the first time, researchers, students, and independent developers can experiment with state-of-the-art coding LLMs on consumer-grade laptops — eliminating the need for multi-GPU server clusters or cloud subscriptions. The technique also opens doors for edge AI applications in low-resource environments, from field engineering to real-time code assistance on mobile workstations.

While the current implementation targets the RTX 3070 Ti, the developer speculates that next-generation hardware like the NVIDIA RTX 4090 or rumored RTX 5090 could push speeds beyond 20 tokens per second, assuming proportional increases in VRAM bandwidth and cache capacity. Early benchmarks suggest that increasing the GPU cache limit from 18 to 120 (corresponding to ~20GB) on higher-end GPUs could maintain cache hit rates above 85%, unlocking near-real-time interaction.

Experts in AI systems architecture have hailed the work as a "masterclass in hardware-aware model optimization." Dr. Elena Vasquez, a researcher at MIT’s Computer Science and Artificial Intelligence Laboratory, commented: "This isn’t just a hack — it’s a paradigm shift. It proves that with architectural insight, we can bypass brute-force hardware demands and unlock efficiency through intelligent data flow design. This could inspire a new generation of lightweight MoE deployment strategies."

The GitHub repository includes full code, configuration scripts, and tuning guidelines for different RAM/VRAM configurations. As of publication, the community has begun replicating the results on AMD and Intel hardware, with early reports indicating promising compatibility with ROCm and oneAPI backends. The success of this project underscores a growing trend: the democratization of AI is no longer dependent solely on hardware scale, but on algorithmic ingenuity.